- HOME

- VENUE

- RSVP

- REGISTRY

- CONTACT

- Adobe premiere pro cs6 error 1

- Zuma deluxe revenge

- Over the garden wall cosplay

- Pokemon emerald randomizer android

- Msi interceptor ds b1 gaming

- 13th film poster

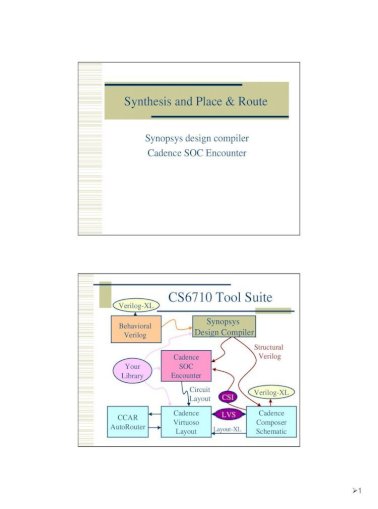

- Synopsys dc

- Young thug barter 6 poster

- Bleach brave souls pvp tier list

- Command and conquer generals zero hour free download full version with crack

- Neo counter strike 1-6

- Sothink logo maker error code 126

- Vmware horizon view client mouse disappears

- Download scribblenauts remix free

- Ic engines pdf

- Delicious emily message in a bottle free download full version

On February 8, 2010, Synopsys announced an acquisition of CoWare. In 2005, CoWare acquired the Signal Processing department from Cadence. CoWare is one of the founding member of SystemC language. In 1996, CoWare spun off as an independent company. CoWare was headquartered in San Jose, California, and had offices around the world, major R&D offices in Belgium, Germany and India.ĬoWare development was initiated by the Interuniversity Microelectronics Centre ( IMEC) in Belgium as an internal project in 1992.

SYNOPSYS DC SOFTWARE

CoWare ĬoWare was a supplier of platform-driven electronic system-level (ESL) design software and services.

SYNOPSYS DC VERIFICATION

Synopsys has made some silicon and design verification acquisitions. The company was initially established as Optimal Solutions with a charter to develop and market synthesis technology developed by the team at General Electric.

You can get a datasheet on Design Compiler NXT here.Synopsys was founded by Aart J de Geus and David Gregory in 1986 in Research Triangle Park, North Carolina. There’s more on Design Compiler NXT from Michael Jackson, corporate vice president, marketing and business development, Synopsys, here from Sassine Ghazi, co-general manager, design group, Synopsys, here, and Abhijeet Chakraborty, group director, R&D, design group, Synopsys, here. This helps avoid the synthesis, place-and-route, and physically-aware signoff-driven ECO processes using different models, in situations in which models are evolving throughout the design process. Correlation between synthesis and place-and-route is further improved by using high-accuracy timing models for path-by-path and endpoint-by-endpoint calculations.ĭesign Compiler NXT also share libraries and block abstract models with IC Compiler II, so that the same libraries can be used for synthesis and place-and-route. This is why Design Compiler NXT has been updated to align the way it undertakes tasks such as estimations of net topology parasitics with the way that IC Compiler does them. These features enable closer correlations between RTL synthesis outputs and layout results. Techniques borrowed from IC Compiler II for concurrent clock and data optimization improve timing and power recovery through dynamic skew management.Īdvanced process nodes have their own design challenges and Design Compiler NXT has features that address these physical issues, including support for creating via pillars, ‘pattern must join’ instances, automatic use of non-default rules, pin-access awareness, variant- aware libraries, layer-aware optimization, and other requirements.

Synopsys also claims that Design Compiler NXT can save up to 5% of dynamic power consumption without degrading timing, area or congestion metrics, by using new techniques for mapping, restructuring, and rewiring.

SYNOPSYS DC FULL

There is also an updated approach to distributed processing: an intelligent partitioner breaks the workload down into smaller jobs and then sends them off to multiple machines for optimization, but ensures each operates with the full physical and logical context of the design.

SYNOPSYS DC CODE

Synopsys claims tool runtimes can be half those of Design Compiler Graphical, thanks to improvements to the core code of the tool and a new approach to multi-threading that improves scalability up to eight cores. The tool also shares libraries and advanced placement technologies with IC Compiler II, in addition to aligned RC, net topology, and density modelling, to enable tighter correlation between the two tools and hence better end results. Synopsys has updated Design Compiler, the IC industry’s RTL synthesis workhorse, to add optimization techniques that speed up its operation and make it suitable for use on designs at process nodes of 5nm and beyond.ĭesign Compiler NXT gains power-driven mapping and structuring techniques, concurrent clock and data (CCD) optimization, and an updated approach to distributed synthesis that does not sacrifice quality-of-results.